# CHAPTER 7

#### Format Examples

#### 7.1 Introduction

This module supplies a flexible software interface between the Floppy Disk Drive(s) and the SCSI bus. This gives a large range of media formats which can be supported.

A separate document called "Floppy Disk Format Examples" will give example drive tables for general media formats.

Use these tables as they are or change them according to your needs.

This Page Intentionally Left Blank

7-2

# CHAPTER 8

#### Hardware Interface

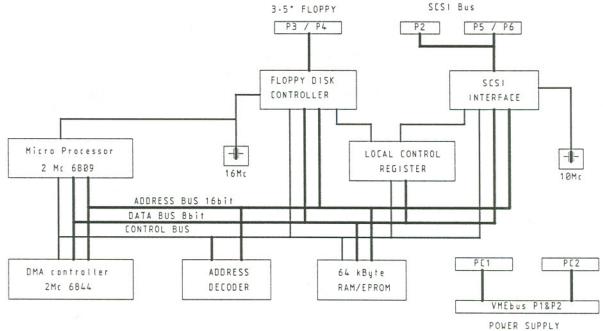

#### 8.1 Features

- 6809 microprocessor ----

- 6844 direct memory controller

- -2 MHz operating frequency

- -64 kBytes of RAM/EPROM on board memory space

- floppy disk drive controller

- SCSI bus controller (target/initiator)

### 8.2 General Description

The CC93 is a high-performance floppy disk drive interface based on the 6809 microprocessor. Data transfer to and from the disk controller and SCSI bus controller may be floppy programmed to occur under DMA control. All devices can interrupt the processor. The board is capable of supporting a total of 64 kByte RAM and EPROM. The amount of EPROM is not restricted. The I/O map can be placed anywhere in the memory-map and takes only 256 bytes of memory. The floppy disk controller can handle all currently known types of floppy disk drives e.g.:

> 8" (DS/DD) 5.25" mini 3.50" micro and 5.25" eight inch compatible.

Mixing of different types of drives is possible. The SCSI bus controller can be used in target mode as well as in initiator mode. In initiator mode other devices may be accessed like e.g. hard disks, tape streamers, other computers etc.. In target mode the single board computer acts as an intelligent interface to the floppy disk drives.

Manual CC93 Ver 2.2

8-1 December 1991

This Page Intentionally Left Blank

## CHAPTER 9

#### Installation Instructions

#### 9.1 Introduction

This chapter provides the hardware preparation and installation instructions for the CC93 module.

## 9.2 Power Connection

Power for the electronics of the board is derived from the P1 and P2 connectors from the VMEbus. Power to the drives can be taken from the PC1 and PC2 connectors:

/\* o o | PC1 and PC2

5V GND 12V

If the total supply current at +12Vdc to the drives does not exceed at any time the maximum current rating for the VMEbus +12Vdc power pin of P1 (about 1.5 Amp at 60 degrees C), then it is not necessary to use the extra pins on the P2 connector. If power does exceed this maximum current (for instance, a hard disk drive at power on), the extra power pins of P2 must be connected externally to the power supply of the VMEbus.

#### 9.3 Jumper Settings

All jumper settings discussed in the next section are illustrated as seen from the component side with the P1 connector downwards. Pin number one is identified as '\*', rest of pins are identified as 'o'.

Manual CC93 Ver 2.2

9-1

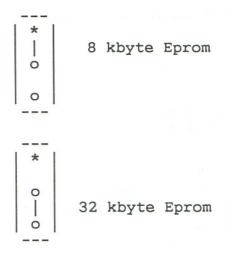

# 9.3.1 JB1: Eprom Size Select

This jumper selects what size of Eprom devices are used.

#### 9.3.2 JB2: Ram Size Select

This jumper selects what size of Ram devices are used.

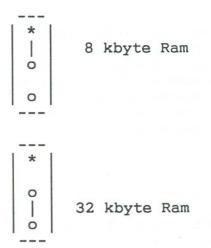

9.3.3 Socket 1

This socket may only contain Ram devices. Jumper blocks JB2 and JB3 must be set according to the size of Ram devices used.

#### JB3: Ram size select

| *0        | 8 kbyte Ram  |

|-----------|--------------|

| 0 0       |              |

| <br>  * o |              |

| 00        | 32 kbyte Ram |

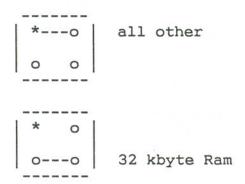

# 9.3.4 Socket 2

This socket may contain Ram or Eprom type of devices. A Ram device must be of the same size as used in Socket 1. An Eprom device must be of the same size as used in Socket 3.

JB4: Ram/Eprom size select

JB5: Ram/Eprom size select

| *0  | 8 kbyte Ram/Eprom  |

|-----|--------------------|

| 0 0 |                    |

| * o |                    |

| 00  | 32 kbyte Ram/Eprom |

Manual CC93 Ver 2.2 9-3

## JB6: Ram/Eprom size select

| *0  | 8/32 kbyte Ram |

|-----|----------------|

| 0 0 |                |

| 0 0 |                |

|     |                |

| * 0 |                |

| 00  | 8 kbyte Eprom  |

| 0 0 |                |

|     |                |

| * 0 |                |

| 0 0 |                |

| 00  | 32 kbyte Eprom |

|     |                |

#### 9.3.5 Socket 3

This socket may only contain Eprom devices. Jumper blocks JB1 and JB7 must be set according to the size of Eprom devices used.

JB7: Eprom size select

\*---0 8 kbyte Eprom 0 0 \* 0 0---0 32 kbyte Eprom

# 9.3.6 JB8: SCSI ID Number

Before connecting the board to a SCSIbus an ID number must be selected. Only one jumper may be installed.

Manual CC93 Ver 2.2

# 9.3.7 JB9: Clock Select

This jumper selects between an 8 or a 10 MHz clock to the NCR5386.

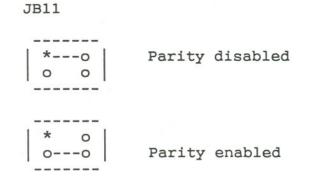

#### 9.3.8 JB11: SCSI Parity Enable

This jumper enables and disables the parity check of the SCSI controller. The controller will however always generate odd parity on all SCSI bus transfers regardless the setting of this jumper. The setting of the jumper is sampled only once when the board is reset. Only one jumper may be installed.

9-5

#### 9.3.9 JB12: Termination Power

When this jumper is removed, the termination power (TRMPWR) for the resistor networks must be supplied via the SCSI bus. When the jumper is installed the resistor networks use the +5V of the board and TRMPWR will be fed to the SCSI bus (using a diode).

#### 9.3.10 JB13/14: Hard Disk ID

The pins of these jumper blocks are one to one connected and allow easy ID change while the Hard Disk drive is mounted.

# 9.4 Connector Assignments

| PIN ASSIGNMENTS |        | P3/P4 |       |           |

|-----------------|--------|-------|-------|-----------|

| 3.50"           | Floppy | disk  | drive | connector |

| D2 /D4       | 2020              |

|--------------|-------------------|

| <u>P3/P4</u> | name              |

| 2            | drive type select |

| 4            | head load         |

| 6            | select 4          |

| 8            | index             |

| 10           | select 1          |

| 12           | select 2          |

| 14           | select 3          |

| 16           | motor on          |

| 18           | direction         |

| 20           | step              |

| 22           | write data        |

| 24           | write enable      |

| 26           | track 0           |

| 28           | write protect     |

| 30           | read data         |

| 32           | side select       |

| 34           | ready             |

| <b>U 1</b>   | 1000J             |

note:

all odd pins are connected to ground.

Manual CC93 Ver 2.2

|                                                                                                                                                                                                                                                 | ASSIGNMENTS<br>bus connector                                                                                                                                                                                                                                                                                                                         | P2 and                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2A<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>9<br>20<br>21<br>23<br>24<br>25<br>24<br>25<br>24<br>25<br>24<br>25<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25 | $     \begin{array}{r} P5/P6 \\       2 \\       4 \\       6 \\       8 \\       10 \\       12 \\       14 \\       16 \\       18 \\       20 \\       22 \\       24 \\       26 \\       28 \\       30 \\       32 \\       34 \\       36 \\       38 \\       40 \\       42 \\       44 \\       46 \\       48 \\       50   \end{array} $ | name<br>-DB(0)<br>-DB(1)<br>-DB(2)<br>-DB(3)<br>-DB(5)<br>-DB(6)<br>-DB(7)<br>-DB(P)<br>GND<br>GND<br>GND<br>GND<br>TRMPWR<br>GND<br>GND<br>-ATN<br>GND<br>-BSY<br>-ACK<br>-RST<br>-MSG<br>-SEL<br>-C/D<br>-REQ<br>-I/O |

note:

pins 1 to 25 of P2C are connected to ground except pin 13, odd pins of P5/P6 are connected to ground except pin 25.

P5/P6

#### CHAPTER 10

#### Theory of Operation

#### 10.1 Introduction

This chapter provides a description of the CC93 floppy interface module. A block diagram is given in appendix A. With the aid of the schematic diagram in appendix B an explanation of the operation is given.

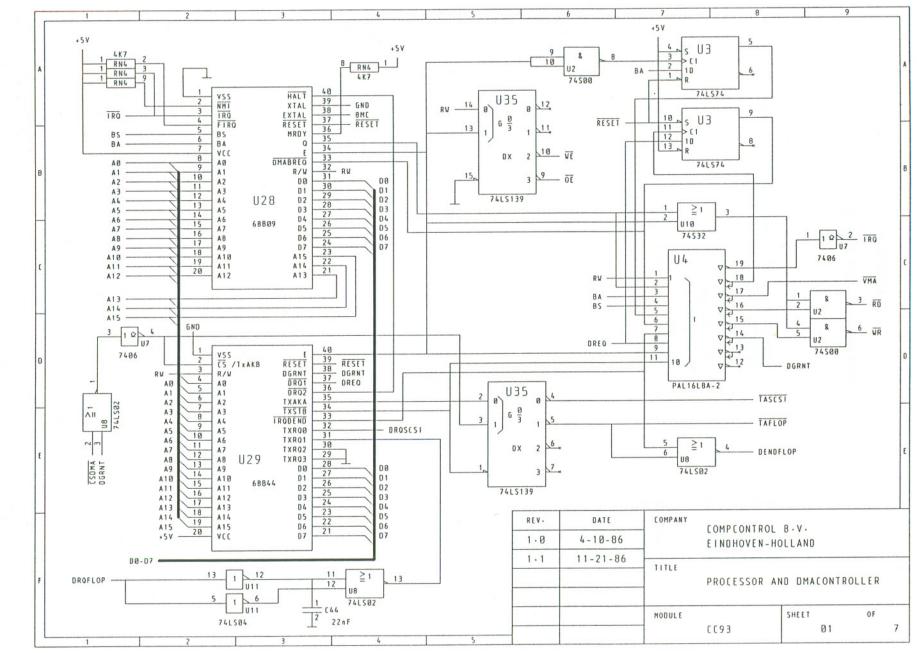

#### 10.2 Central Processor Unit

The implemented microprocessor (U28) is of the type MC68B09.

The chip is supplied with an 8 MHz clock derived from the 16 MHz oscillator (U24) by means of the 74393 counter (U33). The CPU generates two phase shifted 2 MHz clock signals E and Q. All timing of the on board address and databus is related to those two signals.

Inputs to the processor:

/IRQ: is connected to a "wired-or" DMA, Floppy and SCSI interrupt signal

/DMA-BREQ and /HALT are connected to the DMA controller (U29); see appropriate section.

All on board peripherals (except the DMA controller) do not use the Motorola type of bus protocol and an adjustment is made to the R/W generation. Further discussions on this topic are found in the next section.

#### 10.3 Direct Memory Access Controller

The implemented direct memory access controller (U29) is of the type MC68B44.

The controller must be initialized for a DMA transfer by the processor. The data transfer may be either from a peripheral to RAM or from RAM to a peripheral. The controller will take no actions until a peripheral requests a DMA transfer. A peripheral signals the controller that data transfer is wanted by asserting the proper TxRQ (transmit request) line.

The controller then asserts the /DMA-BREQ or /HALT line to the processor to gain control of the bus. The CPU will assert DGRNT (DMA grant) when the bus is available. The controller addresses

Manual CC93 Ver 2.2

the proper RAM location and asserts the TxAK (transmit acknowledge) line to the peripheral which asked for service. The data will be transferred directly between the peripheral and RAM.

The bus is released by the DMA controller after the transfer has taken place and normal CPU operation will continue.

Peripherals serviced by the DMA controller are the Floppy disk drive controller and the SCSI bus controller.

Both the 6809 and the 6844 use R/W to determine the direction of data transfer and use the select line to the peripheral and the E clock to strobe the data transfer. All the other controller circuits use an other type of protocol. They expect two signals apart from the select line: /RD (read peripheral) and /WR (write peripheral). Transfer direction and timing are combined in these signals. The Pall6L8 (U4) is programmed to generate these signals using the R/W line and E and Q clocks. During DMA transfer reading from a peripheral has to be combined with writing to RAM and writing to a peripheral with reading from RAM. To accomplish this an exchange is made to the /RD and /WR signals when in DMA mode (programmed within the Pall6L8 (U4) ).

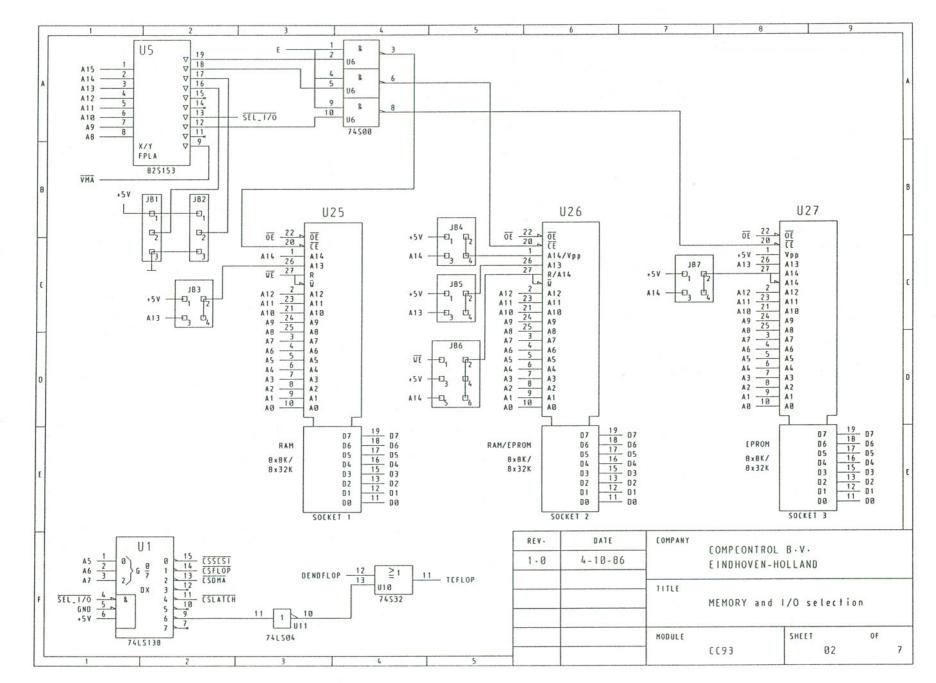

### 10.4 Memory and I/O Selection

The memory map consists of three blocks; an EPROM block, a RAM block and an I/O block. Decoding is done on 256 Byte boundaries. The EPROM area is located at the top of the memory map.

There are three sockets (U25-U27) available in which either 8k or 32k RAM or EPROM memory devices may be inserted. Three sockets are provided to make it possible to locate the EPROM lower boundary on any 256 byte boundary without loosing the unused Eprom area for RAM.

The location of the I/O block is independent of the location of the RAM and EPROM blocks and may be configured anywhere in the map. The total occupied area for I/O is only 256 bytes of memory.

Location of the I/O block and the EPROM lower boundary is programmed within the FPLA (U5). See appropriate section.

10-2

Eight select signals are generated in the decoder (U1). Five are used for selecting:

the SCSI bus controller (U16)

the Floppy disk controller (U30)

the DMA controller (U29)

the Local Control Register (U12-U13)

the Floppy disk controller terminal Count pin (U30)

The remaining select lines are not used.

Each select signal decodes a 32 byte area in the I/O map.

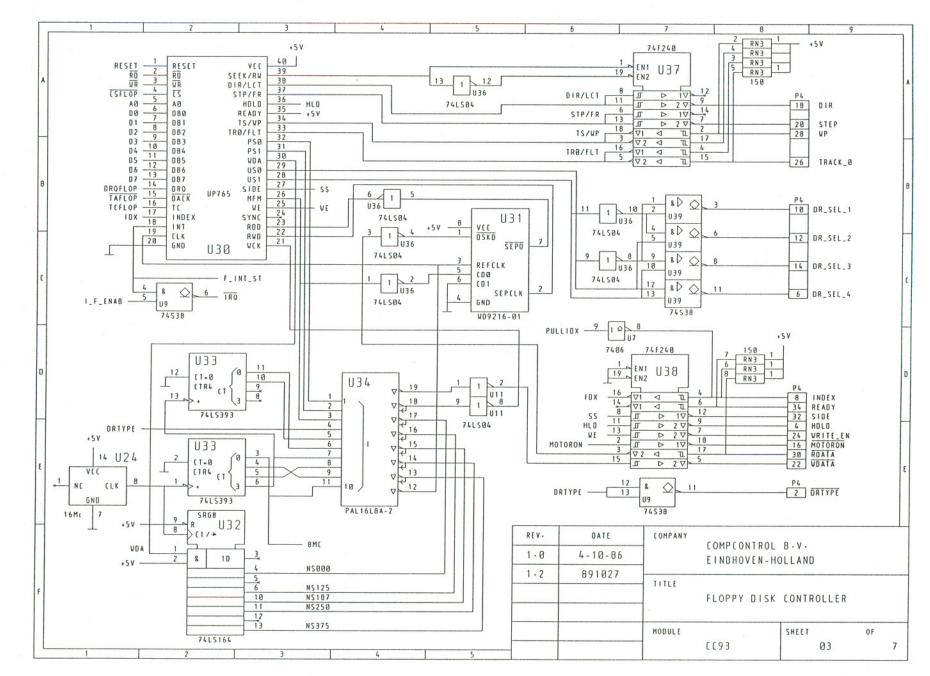

## 10.5 Floppy Disk Interface

The CC93 uses the 16 Mhz clock oscillator circuit (U24) as the base for the signals for writing and formatting sectors. The clock frequency applied to the floppy disk controller (U30) is 8 MHz in 8 inch mode and 4 MHz in 5.25 inch mode. The incoming data from the floppy disk drive is converted by a WD9216/01 data separator (U31) in two separate signals: RDW (read data window) and RDD (read data). The 16 MHz clock is divided into 8, 4, 2, 1 MHz and 500, 250 kHz signals (U33). These signals are supplied to the Pall6L8 (U34) which generates the correct write clock dependent on the density and drive type.

The write data from the floppy disk controller is clocked into an eight bit serial in parallel out shift register (U32) in order to generate the proper preshift delays. The delay time depends on the signals PO, P1 and MFM from the controller (U30) and the drive mode from the Local control register (U12-U13).

The processor must write command bytes into the FDC. After receiving the last command byte, the FDC starts executing the command. Data may be transferred under control of the DMA controller.

### 10.6 SCSI Bus Interface

The interface uses the SCSI bus controller chip NCR5386 (U16). A correct functioning of the interface as defined by the ANSI X3T9.2 committee is thereby guaranteed. For details concerning the programming of the chip see the NCR5386 SCSI Protocol Controller Data Sheet.

A jumperblock (JB 8) must be used for the selection of an ID number.

### 10.7 Local Control Register

An eight bit latch is used as a control register for several purposes.

# The meaning of the used bits are respectively:

| Bit | 0 | selection of drive type 5.25"              |

|-----|---|--------------------------------------------|

| Bit | 1 | turn motor on 5.25" drive                  |

| Bit | 2 | enable the interrupt of floppy interface   |

| Bit | 3 | read the floppy interface interrupt status |

| Bit | 4 | not used                                   |

| Bit | 5 | not used                                   |

| Bit | 6 | read the SCSI interface interrupt status   |

| Bit | 7 | SCSI parity enable                         |

December 1991

Manual CC93 Ver 2.2

# CHAPTER 11

# Programming Considerations

## 11.1 Memory Map

A possible configuration of the memory map is given below. The memory map is divided in three parts:

|            | 0000 |

|------------|------|

| RAM MEMORY | 3FFF |

| I/O AREA   | F000 |

| 1/0 AREA   | FOFF |

| EPROM AREA | E000 |

| EPROM AREA | FFFF |

|            | 7.M  |

| RAM   | \$0000 - \$3FFF | 16 kBytes                |     |

|-------|-----------------|--------------------------|-----|

| I/O   | \$F000 - \$F0FF | 256 Bytes                |     |

| EPROM | \$E000 - \$FFFF | 8 kBytes - 256 Bytes (I/ | (0) |

Using the lower boundary of the I/O map as the baseaddress, the peripherals are located as follows:

offset

| SCSI control                    | base address + \$00 |

|---------------------------------|---------------------|

| 16 registers                    |                     |

| Floppy control                  | base address + \$20 |

| 2 registers                     |                     |

| DMA control                     | base address + \$40 |

| 22 registers                    |                     |

| not used                        | base address + \$60 |

| Local Contr. R.                 | base address + \$80 |

| 1 register                      |                     |

| not used                        | base address + \$A0 |

| Terminal Count<br>Floppy Contr. | base address + \$CO |

| not used                        | base address + \$E0 |

Both the location of the I/O block and the EPROM and RAM boundaries may be changed to accommodate personal needs. See APPENDIX E for details on this subject.

Use I/O baseaddress + I/O base offset as a base address for addressing the registers in the peripherals.

### 11.2 DMA Controller

The 6844 is capable of supporting up to four different peripherals (channels).

The assignment of the channels is as follows:

| channel | 0 | SCSI bus controller    |

|---------|---|------------------------|

| channel | 1 | Floppy disk controller |

| channel | 2 | not used               |

| channel | 3 | not used               |

Three modes of data transfer are programmable in the 6844:

Manual CC93 Ver 2.2

11-2

Mode 1 and Mode 2 are single byte transfers;

Mode 1: uses the cycle steal mode by asserting the /DMA-BREQ line to the processor

Mode 2: uses the halt steal mode by asserting the /HALT line to the processor

Mode 3 is a burst transfer mode which uses the halt steal mode by asserting the /HALT line to the processor.

The interrupt output is "wired-or" connected to the /IRQ input of the CPU.

The 22 registers of the 6844 are addressed at I/O baseaddress + \$40 + register address

For programming the 6844 see Motorola 8 Bit Microprocessors Data Manual.

### 11.3 Floppy Disk Controller

The uPD765 is capable of controlling up to four floppy disk drives.

Normally all four drives should be of the same type (8" or 5.25") due to the fact that both types use different data transfer rates. By controlling the clock frequency to the FDC through a software switch (local control register bit 0) it is made possible to interface to both types without making hardware changes. This bit also controls the level of pin 2 of the 5.25" FDD connector (P4). This provides a means of signalling the FDD to change from 5.25" to 8" mode.

Also it is possible to turn the motor on and off (local control register bit 1).

It is not possible to enable/disable the interrupt output in the uPD765 internally. Therefore a software switch is provided to control the interrupt output enable (local control register bit 2).

It is not possible to determine if the FDC has asserted the interrupt output through reading a single register of the controller. By reading local control register bit 3 the status of the interrupt output is available to the CPU.

When using the FDC in Non-DMA mode the TC pin (Terminal Count) of the FDC must be asserted by the processor. Accessing the I/O memory with an offset of \$CO to \$DF will assert the TC pin of the FDC. When using the FDC in DMA mode the DMA Controller will assert the TC pin.

Summery of bits in the local control register used for controlling the FDC.

Manual CC93 Ver 2.2

11-3

Bit 0: 0 drive type is 8" 1 drive type is 5.25" this bit is read/write used for switching between 8" and 5.25" drives

- Bit 1: 0 motor off 5.25" drive 1 motor on 5.25" drive this bit is read/write used to turn motor on and off when interfacing to 5.25 " type of drive

- Bit 2: 0 interrupts from FDC disabled 1 interrupts from FDC enabled this bit is read/write used to prevent the FDC from generating interrupts

- Bit 3: 0 interrupt output FDC is not asserted 1 interrupt output FDC is asserted this bit is read only used to determine if FDC is source of interrupt

All write bits are reset during system reset

The interrupt output is "wired-or" connected to the /IRQ input of the CPU.

The 2 registers of the uPD765 are addressed at I/O baseaddress + \$20 + register address

For programming the uPD765 see NEC Data Sheets.

### 11.4 SCSI Bus Controller

The NCR5386 operates in both the initiator and the target roles and can therefore be used in host adapter and control unit designs. The device supports arbitration, including reselection.

It is not possible to determine if the SCSI controller has asserted the interrupt output through reading a single register of the controller without loosing some information about the interrupt (see data sheet NCR5386). By reading local control register bit 6 the status of the interrupt output is available to the CPU.

Bit 7 in the local control register can be used to read the parity enable jumper JB11. It can be sampled by the software to determine if parity on the SCSI bus should be checked or not.

Summery of bits in the local control register used for the SCSI bus controller.

Bit 6: 0 interrupt output SCSI controller is not asserted 1 interrupt output SCSI controller is asserted this bit is read only

Manual CC93 Ver 2.2

used to determine if SCSI bus controller is source of interrupt

#### 0 parity should be checked Bit 7: parity should not be checked 1 this bit is read only used to determine if parity should be checked on the SCSI bus

The interrupt output is "wired-or" connected to the /IRQ input of the CPU.

The 16 registers of the NCR5386 are addressed at I/0 baseaddress + \$00 + register address

For programming the NCR5386 see NCR5386 Protocol Controller Data Sheet.

11.5 Local Control Register

This register is used to control and monitor several functions of the board. A brief description of the use of the different bits is given here; for details see appropriate sections.

The Local Control Register is addressed at I/O baseaddress + \$80.

Summery of bits in the local control register used for controlling the FDC.

- drive type is 8" Bit O: 0 1 drive type is 5.25" this bit is read/write used for switching between 8" and 5.25" drives

- Bit 1: 0 motor off 5.25" drive motor on 5.25" drive 1 this bit is read/write used to turn motor on and off when interfacing to 5.25 " type of drive

- Bit 2: 0 interrupts from FDC disabled 1 interrupts from FDC enabled this bit is read/write used to prevent the FDC from generating interrupts

- Bit 3: 0 interrupt output FDC is not asserted 1 interrupt output FDC is asserted this bit is read only used to determine if FDC is source of interrupt

Summery of bits in the local control register used for the SCSI bus controller.

| Bit | 6: | 0 | interrupt output SCSI controller is not asserted |

|-----|----|---|--------------------------------------------------|

|     |    | 1 | interrupt output SCSI controller is asserted     |

|     |    |   | this bit is read only                            |

|     |    |   | used to determine if SCSI bus                    |

|     |    |   | controller is source of interrupt                |

|     |    |   |                                                  |

Bit 7: 0 parity should be checked 1 parity should not be checked this bit is read only used to determine if parity should be checked on the SCSI bus

# APPENDIX A

BLOCK DIAGRAM

DRIVES and LOGIC

Appendix CC93

This Page Intentionally Left Blank

Appendix CC93

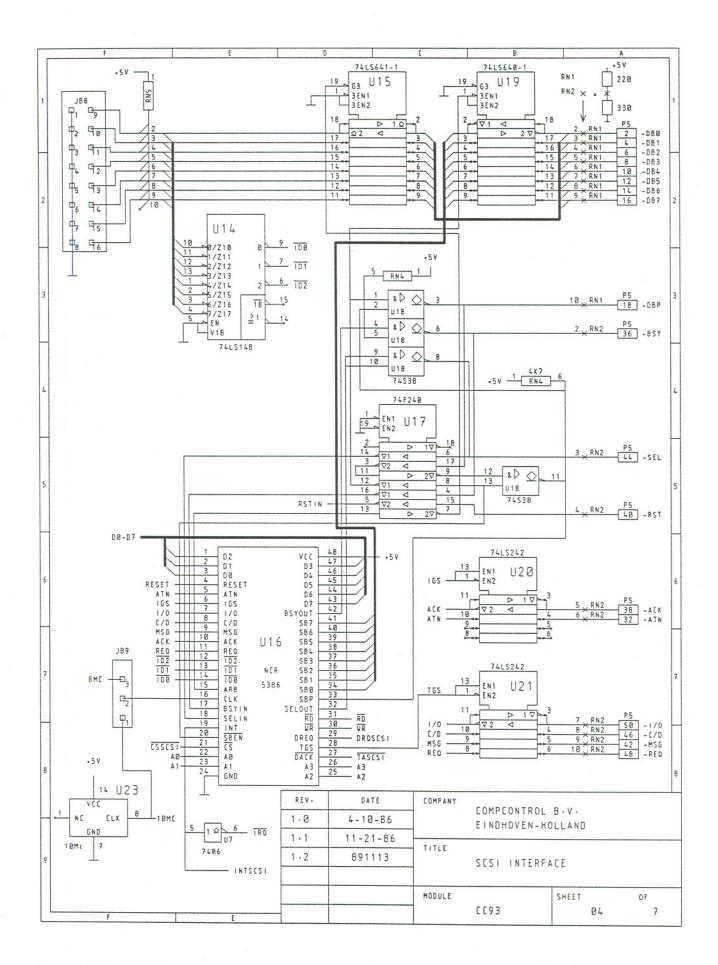

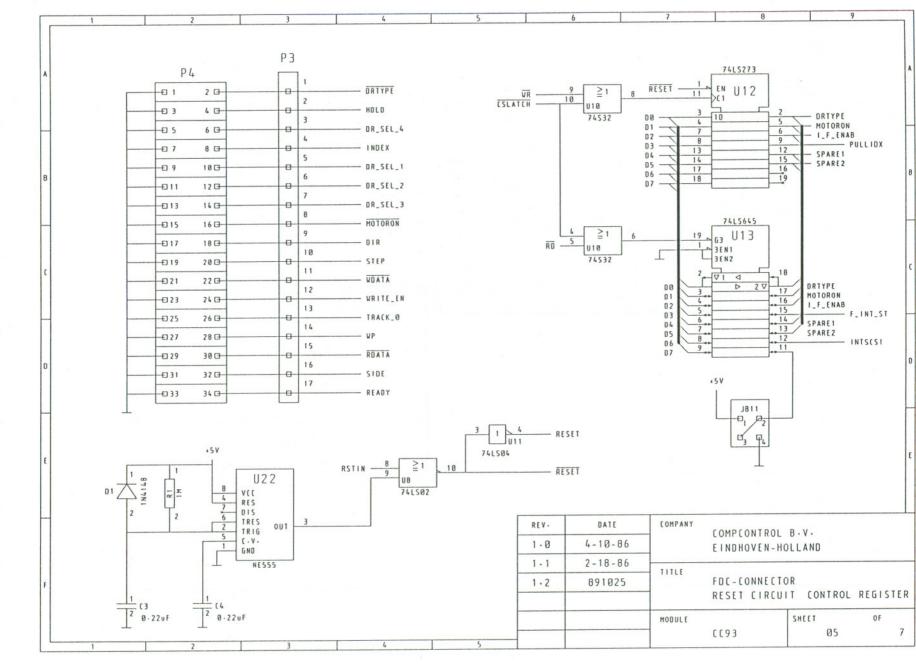

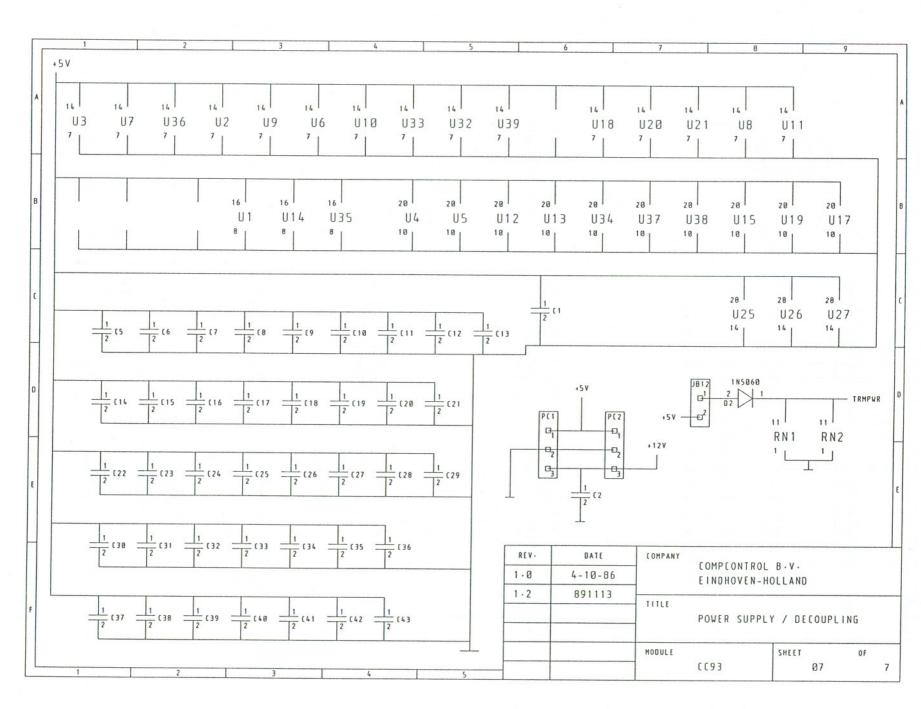

#### APPENDIX B

# SCHEMATIC DIAGRAMS

Sheet 1Processor and dma controllerSheet 2Memory and I/O selectionSheet 3Floppy disk controllerSheet 4SCSI interfaceSheet 5FDC connector /Reset circuit /Control registerSheet 6VMEbus and SCSIbus connectorsSheet 7Power supply decoupling

B-2

B-3

B-4

в-6

|      | * 8   | -    | 12   | 6     | 11    | 85 8.  | -086 | -087   | -06P  |        | 0      | 0     | TRMPUR |         |        | -ATN 0 |        |          | - 416      |       |      | -564  | Bro  | 0/1-    | 4    |      |       |                 | 9      | 1       |                                       |         |                    |     |        |

|------|-------|------|------|-------|-------|--------|------|--------|-------|--------|--------|-------|--------|---------|--------|--------|--------|----------|------------|-------|------|-------|------|---------|------|------|-------|-----------------|--------|---------|---------------------------------------|---------|--------------------|-----|--------|

|      | -088  | 081  | -082 | -083  | -084  | -085   |      |        |       | 11 GND | 12 GND |       |        | 15 GND  |        |        | 18 CND | 19       | 28         | 12    | 22   | 1     | 24   | 22      |      |      |       |                 |        |         |                                       |         | SCSIbus connectors | -   | 10     |

| P.6. | -     | D    | -    | 0     | 0     | 0      | •    | 0      | 0     | 0      | 0      | •     |        | +       | +      | +      | +      |          | +          |       |      | 0 0   | -    |         | ]    |      | Ъ     | °e <sub>1</sub> | °e-    |         | AND                                   |         | 015 (01            | 111 | SHEET  |

|      |       |      |      |       |       |        |      |        |       |        |        |       |        |         |        |        |        |          |            |       |      |       |      |         |      | 1-   |       |                 | 4      |         | COMPCONTROL B.V.<br>FINDHOVEN-HOLLAND |         | 05                 |     | ~      |

| 5    | 10 2  | 1 0  | 6 9  | 8 (3- | 1813  | 12 (3- | 11.0 | 16 []- | 18 [] | 2813-  | 22 0-  | 14 0- | 260    | 28 G    | 30 G   | 32 G-  | 34.0-  | 36 (3-   | 86         | -E 87 | 120- | -011  |      | 580     |      | 1813 | 20 19 | -0-             | 30 50  |         | F I NDH                               |         | VMEbus             |     |        |

| PS   | - 0   | 0.3  | 5 0  | 10    | 6 0   | 10     | 610  | 015    | 110   | 610    | 120    | 67.0  | -025   | 120     | 029    | 1031   | 6033   | -035     | 160        | 60    | 130  | 610   |      | 610     |      |      |       |                 |        | COMPANY |                                       | TITLE   |                    |     | MODULE |

|      | GND T | GND  | GND  | 0ND   | 6ND   | 6ND    | GND  | GND    | 6 ND  | GND    | GND    | 6ND   | 1      | 6ND     | 6ND    | 6ND    | CND    | 6ND      | 6ND        | 0ND   | 6ND  | GND   | 0.0  | CND CND |      | ł    |       |                 |        |         | 1                                     |         |                    |     | M      |

|      | 9     | 5    | 9    | 9     | 9     | 9      | 0    | 0      |       | 0      | 0      |       |        |         | 2      |        |        |          |            |       |      |       |      |         |      |      |       |                 |        | DATE    | 4-10-86                               | 2-19-87 | 891113             |     |        |

|      |       |      |      |       |       |        |      | ie '   | -     | I      |        |       |        |         |        |        |        |          |            |       |      |       | -    |         |      |      |       |                 |        | REV.    | 1.8                                   | 1.1     | 1.2                |     |        |

| P2C  | GND   | GND  | GND  | GND   | GND   | GND    | GND  | GND    | GND   | GND    | GND    | GND   |        | GND     | GND    | GND    | GND    | GND      | GND        | GND   | GND  | GND   | GND  | GND     |      | GND  | GND   | GND             | GND    | GND     | GND                                   |         |                    |     |        |

|      | -     | 2 0  | 9    | 9     | 5 0   | 9      | 1 0  | 8      | 6     | 18 10  | -      | 12 0  | 13     | 14 0    | 15 10  | 16 10  | 17 0   | -        | 6          | -     |      | 0 12  | 1    | 25 0    | 26 0 | 27 0 | 28 0  | 29 Đ            | 38 10  | 31      | 32 0                                  |         |                    |     |        |

| P2B  | .5V   | GND  |      |       |       |        |      |        |       |        |        | GND   | + 5 V  |         |        |        |        |          |            |       |      | GND   |      |         |      |      |       |                 |        | GND     | •5V                                   |         |                    |     |        |

|      | -     | 2 0  | 3 0  | -     | 2     | 9      | 0 /  | 0      | 9 6   | 18     | P<br>= | 12 0  | 6      | 1       | 12     | 9      | 11-10  | <b>q</b> | -          | 1     | 0    | -     | 0 1  | 25 0    | 26 0 | 11 0 | 28 0  | 29 10           | 38 -61 | 31 8    | 32 0                                  |         |                    |     |        |

| PZA  | - 049 | -081 | -082 | -083  | - 084 | -085   | -086 | -087   | -08P  | GND    | GND    | GND   | TRMPUR | 0       | GND    | -ATN   | GND    | -85Y     | - A( K     | -851  | -MSG | - 561 | -1/0 | -810    |      | ¥2V  | +5V   | +5V             | •12V   | •124    | •124                                  |         |                    |     |        |

| d.,  | -     |      |      | 9     | -     | -      |      | -      | 9     | P      | P      | 9     | 9      | END GND | 9      | -      | 9      | 9        | 9          | 7     | 9    | -     | 9    |         | P    | 9    | 9     | P               | 9      | 9       | 9                                     |         |                    |     |        |

|      | -     | 2    |      | -     | ~     | •      | ~    |        | 6     | °      | =      | 2     | =      | =       | £ <br> | 2      | =      | 8        | 6-         |       | ~    |       |      | 32      | 26   | 21   | 28    | 29              | 8      |         | 2                                     |         |                    |     |        |

| PIC  |       |      |      |       |       |        |      |        | GND   |        |        |       |        |         |        |        |        |          |            |       |      |       |      |         |      |      |       |                 |        | +12V    | •54                                   |         |                    |     |        |

|      | -     | 2    |      |       |       | 9      | 0 /  | -      | 6     | 18     | =      |       |        | 0 11    |        | 16 0   |        | -        | 61         | -     | 21 0 | -     | ++   | 25 0    |      | 27 0 | 28 0  |                 | 38 10  | 31 8    | 32 10                                 |         |                    |     |        |

| P18  |       |      |      |       |       |        |      |        |       |        |        |       |        |         |        |        |        |          |            | GND   |      |       | GND  |         |      |      |       |                 |        |         | •5V                                   |         |                    |     |        |

|      | -     | 2    |      | -     | 2     | 9      | -+   | 9      | 9 6   | 18 10  | -      | 12 -0 | 13 0   |         | 15 8   | 16 0   | 11 0   | 18       | 1 <u>9</u> | 28 10 | 21 0 |       |      | 25 0    | 26 5 |      | 28 0  | 29 - 10         | 38     | 31 0    | 32 0                                  |         |                    |     |        |

| PIA  | Γ     |      | Τ    |       |       |        |      |        |       |        |        |       |        |         |        |        | 0      |          |            |       |      |       |      |         |      |      |       |                 |        |         | >                                     |         |                    |     |        |

| Р    |       |      |      |       |       | -+     | -+   | -+     |       | 9      |        | 0     | 0      | 9       | 049 0  | 9      | E 640  | 9        | EI GND     |       | P    |       |      | +       |      | -+-  | -     |                 | -      |         | +                                     |         |                    |     |        |

|      | -     | ~    | ~    | -     | 5     | 9      | ~    |        | 6     | 8      | =      | 12    | 13     | =1      | 15     | =1     | =      | =1       | 19         | 28    | 21   | 22    | 5    | 25      | 26   | 27   | 28    | 29              | 38     | 12      | 32                                    |         |                    |     |        |

December 1991

B-8

2

## APPENDIX C

Appendix CC93

#### APPENDIX C

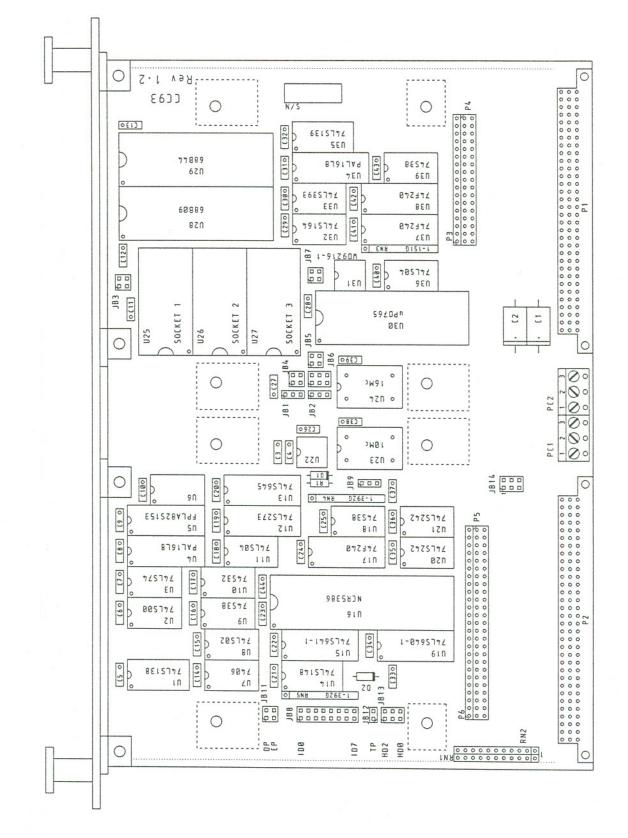

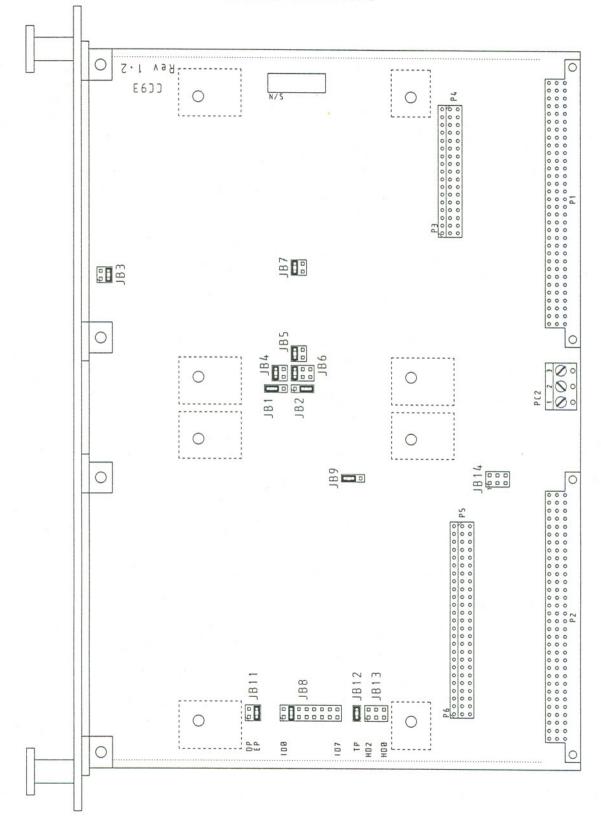

#### JUMPER LOCATIONS

Appendix CC93

## APPENDIX D

## LIST OF COMPONENTS

# Integrated Circuits (TTL)

| U7<br>U8<br>U9<br>U10<br>U11<br>U12<br>U13<br>U14<br>U15<br>U17<br>U18<br>U19<br>U20,U21<br>U31<br>U32<br>U33<br>U35<br>U36<br>U37,U38 | 74LS138<br>74S00<br>74LS74<br>74S00<br>74O6<br>74LS02<br>74S38<br>74S32<br>74LS04<br>74LS273<br>74LS645<br>74LS148<br>74LS641-1<br>74F240<br>74S38<br>74LS641-1<br>74F240<br>74S38<br>74LS640-1<br>74LS640-1<br>74LS164<br>74LS393<br>74LS139<br>74LS139<br>74LS04<br>74F240<br>74S38 | BUS TRANCEIVER<br>DATA SEPARATOR<br>SHIFT REGISTER<br>COUNTER<br>DECODER<br>INVERTER<br>BUFFER |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                                                                                                                                        |                                                                                                                                                                                                                                                                                       |                                                                                                |

| U39                                                                                                                                    | 74S38                                                                                                                                                                                                                                                                                 | BUFFER<br>NAND GATE                                                                            |

| Integrated                                                                                                                             | Circuits (PLD)                                                                                                                                                                                                                                                                        |                                                                                                |

| U4                                                                                                                                     | 16L8A-2                                                                                                                                                                                                                                                                               | PAL                                                                                            |

| 04  | 16L8A-2 | PAL  |

|-----|---------|------|

| U5  | 82S153  | FPLA |

| U34 | 16L8A-2 | PAL  |

Integrated Circuits (Miscellaneous)

| U30 UPD765 FD CONTROLLER | U16 | NCR5386   | SCSI CONTROLLER |

|--------------------------|-----|-----------|-----------------|

|                          | U22 | NE555     | TIMER           |

|                          | U23 | KXO-01-10 | CLOCK OSCILLATO |

|                          | U24 | KXO-01-16 | CLOCK OSCILLATO |

|                          | U28 | 68B09     | MICROPROCESSOR  |

|                          | U29 | 68B44     | DMA CONTROLLER  |

|                          | U30 | UPD765    | FD CONTROLLER   |

# Memory Devices

| U25-U27 0-0 | 640362-3 |

|-------------|----------|

|-------------|----------|

28 PIN SOCKET

Appendix CC93

# Capacitors

| C1,C2  | 100 uF    | Capacitor, electrolytic |

|--------|-----------|-------------------------|

| C3,C4  | 220NF/63V | Capacitor               |

| C5-C43 | 0.1 uF    | Bypass capacitor        |

| C44    | 22NF      | Capacitor               |

# Resistors

| R1 | 1 MOhm |

|----|--------|

|    |        |

Resistor

Resistor Networks

| RN1, RN2 | 4611X-104-221/331 | 220/330 Ohm, 11-pin SIP |

|----------|-------------------|-------------------------|

| RN3      | DALE 1-151G       | 150 Ohm, 10-pin SIP     |

| RN4,RN5  | MSP10A01-392G     | 3.9 KOhm, 10-pin SIP    |

### Miscellaneous

| D1<br>D2<br>JB1,JB2<br>JB3-JB5<br>JB6<br>JB7<br>JB8<br>JB9<br>JB11<br>JB12<br>JB13<br>JB14 | 1N4148<br>BYV10-30<br>3-pin<br>4-pin<br>6-pin<br>16-pin<br>3-pin<br>4-pin<br>2-pin<br>6-pin | DIODE<br>DIODE<br>Jumper block (1 x 3)<br>Jumper block (2 x 2)<br>Jumper block (2 x 3)<br>Jumper block (2 x 2)<br>Jumper block (hor) (2 x 8)<br>Jumper block (hor) (2 x 2)<br>Jumper block (hor) (2 x 1)<br>Jumper block (hor) (2 x 3) |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1, P2                                                                                     | 6-pin<br>96-pin                                                                             | Jumper block (hor) (2 x 3)                                                                                                                                                                                                             |

|                                                                                            | -                                                                                           | IEC-603 male connector                                                                                                                                                                                                                 |

| P3, P4                                                                                     | 34-pin                                                                                      | Jumper block (hor) (2 x 17)                                                                                                                                                                                                            |

| P5,P6                                                                                      | 50-pin                                                                                      | Jumper block (hor) (2 x 25)                                                                                                                                                                                                            |

| PC1, PC2                                                                                   | WKS 17-06-A                                                                                 | T&B POWER CONNECTOR                                                                                                                                                                                                                    |

#### APPENDIX E

#### MEMORY MAP

A description is given of the use of the F82S153 and the programming of this device.

|     |    | \ | /- |    |         |

|-----|----|---|----|----|---------|

|     |    | \ |    |    |         |

| A15 | 1  |   |    | 20 | VCC     |

| A14 | 2  |   |    | 19 | SOCKET1 |

| A13 | 3  |   |    | 18 | SOCKET2 |

| A12 | 4  |   |    | 17 | RAM8    |

| A11 | 5  |   |    | 16 | EPROM8  |

| A10 | 6  |   |    | 15 | RAM     |

| A9  | 7  |   |    | 14 | EPROM   |

| A8  | 8  |   |    | 13 | IO      |

| VMA | 9  |   |    | 12 | SOCKET3 |

| GND | 10 |   |    | 11 | NC11    |

|     |    |   |    |    |         |

|     |    |   |    |    | -       |

F82S153

For the three signals /IO, /EPROM and /RAM addresslines A8-A15 and /VMA are used to decode the three parts of memory. Highest priority has the /IO signal. When /IO becomes active neither /RAM nor /EPROM may become active. All outputs are active low.

- EPROM MAP: choose a lower boundary address for the EPROM map. Program /EPROM to be active on all addresses higher than and the same as this lower boundary.

- RAM MAP: choose a upper boundary address for the RAM map. Program /RAM to be active on all addresses lower than this upper boundary.

- IO MAP: use all eight addresslines A8-A15 to define an IO base address. A block of 256 bytes is now reserved for I/O; this block of memory is automatically locked out for RAM or EPROM.

Appendix CC93

```

FPLA specifications used for example memory map.

module PAL1;

flag '-r3', '-V', '-XH';

title 'MEMORY SELECTOR COMPCONTROL B.V. EINDHOVEN';

"PAL DESIGN SPECIFICATIONS J.H. BRAND 2-4-1986

C93P1R0 device 'F82S153';

"declarations

H, L = 1, 0;

X = .X.;

A15, A14, A13, A12, A11, A10, A9, A8, VMA

1, 2, 3, 4, 5, 6, 7, 8, 9;

pin

EPROM8, RAM8

16,

17;

pin

GND, VCC

10, 20;

pin

IO, EPROM, RAM

13,14, 15;

pin

SOCKET3, SOCKET2, SOCKET1

pin

12, 18, 19;

NC11

pin 11;

address = [A15, A14, A13, A12, A11, A10, A9, A8, X, X, X, X, X, X, X, X];

equations

"EXAMPLE CONFIGURATION: ---8 kbyte ROM--- ---16 kbyte RAM--- ---

IO = F000-F0FF EPROM <= E000

RAM <= 3FFF

(address>= hF000) & (address<= hF0FF);</pre>

!IO

= !VMA &

!EPROM = !VMA & IO & (address>= hE000) & (address<= hFFFF);</pre>

!RAM

= !VMA & IO & (address>=^h0000) & (address<=^h3FFF);</pre>

"socket equations are not altered for other memory configurations!!

"_____!!

SOCKET1 = !RAM & !RAM8

& (address>=^h0000) & (address<=^h7FFF)

# !RAM & RAM8 & (address>=^h0000) & (address<=^h1FFF);</pre>

SOCKET2 = !RAM & !RAM8 & (address>= h8000) & (address<= hFFFF)

# !RAM & RAM8 & (address>=^h2000) & (address<=^h3FFF)

# !EPROM & !EPROM8 & (address>=^h0000) & (address<=^h7FFF)</pre>

# !EPROM & EPROM8 & (address>=^hC000) & (address<=^hDFFF);</pre>

SOCKET3 = !EPROM & !EPROM8 & (address>=^h8000) & (address<=^hFFF)

# !EPROM & EPROM8 & (address>=^hE000) & (address<=^hFFFF);</pre>

```

```

end PAL1;

```